- Home

- Documentation

- Community

- Projects

- Boards

- Agilex 5 SoC

- Agilex 7 SoC

- Arria 10 SoC

- Nallatech 385A - Arria 10 FPGA Network Accelerator Card

- Nallatech 385A-SoC Accelerator Card with Arria 10 FPGA

- ALARIC Instant DevKit ARRIA 10 SoC FMC IDK by REFLEX CES

- Altera Arria 10 SoC Virtual Platform

- Altera Arria 10 SoC Board

- Nallatech 510T compute acceleration card with Intel Arria 10 FPGA

- REFLEX CES Achilles Arria 10 SoC SOM

- Terasic Arria10 SoC Board : HAN Pilot Platform

- Arria V SoC

- Cyclone V SoC

- Altera Cyclone V SoC Board

- Arrow SoCKit User Manual - July 2017 Edition

- Arrow SoCKit User Manual - November 2019 Edition

- Arrow SoCKit Evaluation Board

- Atlas-SoC Development Platform

- Critical Link MitySOM-5CSx Development Kit

- Cyclone V Ethernet driver problems

- DE10-Nano Development Board

- Terasic DE10-Standard Development Kit

- Devboards DBM-SoC1 module

- Devboards DBM-SoC2 module

- EBV SoCrates Evaluation Board

- Enclustra Mercury SA1 SoC Module

- Enterpoint Drigmorn 5

- Enterpoint Larg 2

- Altera Cyclone V SoC Development Platform

- Mpression Helio SoC Evaluation Kit by Macnica

- Mpression Sodia Evaluation Board by Macnica

- ARIES Embedded - MCV System on Module

- Mpression Borax SOM Module and Development Kit by Macnica

- Enterpoint Mulldonoch 3

- Networked Pro-Audio FPGA SoC Development Kit by Coveloz

- NOVPEK™CVLite

- NOVSOM®CV

- NOVSOM®CVLite

- NovTech IoT Octopus™

- NovTech NetLeap™

- Enterpoint Raggedstone 4

- Solectrix SMARC compliant System-on-Module

- Terasic DE1-SoC Development and Education Board

- Stratix 10 SoC

- Find a Board

- News

Documentation

Similar topics

-

GSRD v15.1 - Using System Console - Arrow SoCKit Edition

GSRD v15.1 - Using System Console - Arrow SoCKit Edition

-

GSRD v15.0 - Using System Console - Arrow SoCKit Edition

GSRD v15.0 - Using System Console - Arrow SoCKit Edition

-

GSRD v16.0 - Using System Console - Arrow SoCKit Edition

GSRD v16.0 - Using System Console - Arrow SoCKit Edition

-

GSRD System Console - Arrow SoCKit Edition

GSRD System Console - Arrow SoCKit Edition

-

GSRD v14.1 - Using System Console - Arrow SoCKit Edition

GSRD v14.1 - Using System Console - Arrow SoCKit Edition

Recent Changes

-

GSRD for Agilex 7 I-Series Transceiver-SoC DevKit (4x F-Tile)

Golden System Reference Design for DK SI AGI027FB, DK SI AGI027FA and DK SI AGI027FC

GSRD for Agilex 7 I-Series Transceiver-SoC DevKit (4x F-Tile)

Golden System Reference Design for DK SI AGI027FB, DK SI AGI027FA and DK SI AGI027FC -

Macnica Sulfur ~ Development Kit for Agilex™ 5 FPGA E-Series ~

Macnica Sulfur ~ Development Kit for Agilex™ 5 FPGA E-Series ~

-

Building Bootloader for Agilex 5

Building latest bootloaders for Agilex 5 SoC Devices

Building Bootloader for Agilex 5

Building latest bootloaders for Agilex 5 SoC Devices - Ashling RiscFree Examples

-

Intel® Simics® Simulator for Intel FPGAs Release Notes

This page provides release information about the Intel® Simics® simulator for Intel FPGAs.

Table of Contents

Overview

System Console is an FPGA system debugging tool that is part of the Quartus II package. This page demonstrates how to use the System Console to control the development board peripherals:- Turn LEDs on and off

- Read pushbutton values

- Send characters to console through JTAG UART connection

- Read and write to the on-chip memory

Reference Material

For more information about GHRD see GHRD Overview. For more information about System Console, refer toPrerequisites

1. Unzip the GHRD archive cv_soc_devkit_ghrd.tar.gz to the home folder and use the instructions from Compiling the Hardware Design to compile the FPGA design. 2. Program the FPGA using Quartus II Programmer as described in FPGA Programming with Quartus II Programmer. Start System Console 1. Start Quartus II~/altera/14.0/quartus/bin/quartus2. In Quartus II, go to File → Open Project and select the file ~/sockit_ghrd/soc_system.qpf 3. In Quartus II, start the Qsys window by going to Tools → Qsys 4. When Qsys opens, it will ask for a .qsys file. Browse to*~/sockit_ghrd/soc_system.qsys* and click Open 5. In Qsys, go to Tools → System Console

6. Run the pwd command in system console to make sure the current folder is ~/sockit_ghrd/. If it is not, then execute cd command to change the current folder accordingly.

6. Run the pwd command in system console to make sure the current folder is ~/sockit_ghrd/. If it is not, then execute cd command to change the current folder accordingly.

7. Run the GHRD script by typing source ghrd_sc_script.tcl

7. Run the GHRD script by typing source ghrd_sc_script.tcl

Controlling LEDs

The Development Kit has 4 LEDs that are connected to the FPGA. They are D5..D8 marked as FPGA LED 3..0. The LEDs are turned ON by default. 1. Use the following command to turn all LEDs off:led_off2. Turn on LED D5 by typing the following command:

led_on 0x73. Turn on LED D6 by typing the following command:

led_on 0xb4. Turn on LED D7 by typing the following command:

led_on 0xd5. Turn on LED D8 by typing the following command:

led_on 0xe6. Turn all LED on by typing the following command

led_on 0x0

Reading Push Button State

The Development Kit has two push buttons that are connected to the FPGA. The are marked as KEY0 and KEY1. 1. Type the following command to clear the parallel I/O (PIO) data register:button_data_read_clear2. Type the following command to enable interrupts from push button KEY1:

button_intr_enable 0x13. Type the following command to start the interrupt monitoring in System Console:

irq_monitor_onSystem Console will read the push button interrupt status every five seconds and display it on the console. It will initially show the button as not pressed. 4. Press button KEY1 on the development board. The irq monitor will indicate that the button is pressed until a button_data_read_clear will be run to clear the status.

5. Type the following command to turn off interrupt monitoring:

5. Type the following command to turn off interrupt monitoring:

irq_monitor_off

Sending Characters Using JTAG UART

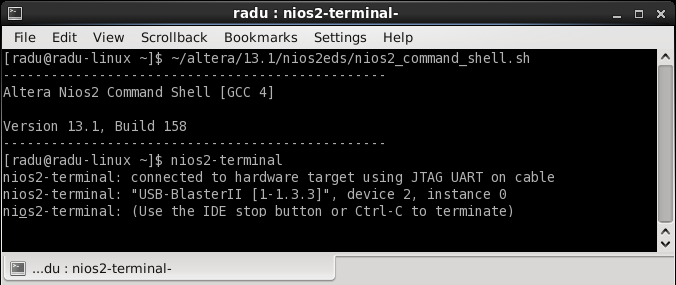

The GHRD contains a JTAG UART sof IP core, that can be used to transfer data between FPGA and the host PC. On the host PC, the data is handled by the nios2-terminal application. 1. Start the nios2-terminalapplication from a NIOS II command shell:$ ~/altera/14.0/nios2eds/nios2_command_shell.sh $ nios2-terminal

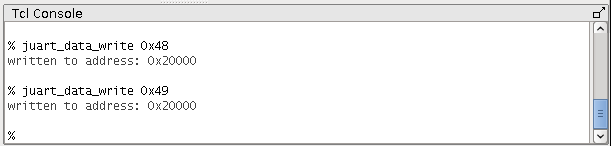

2. In System Console, type the following commands to send characters to the host PC:

2. In System Console, type the following commands to send characters to the host PC:

juart_data_write 0x48 juart_data_write 0x49

3. The NIOS Console will display the two characters that were sent, spelling the word "HI":

3. The NIOS Console will display the two characters that were sent, spelling the word "HI":

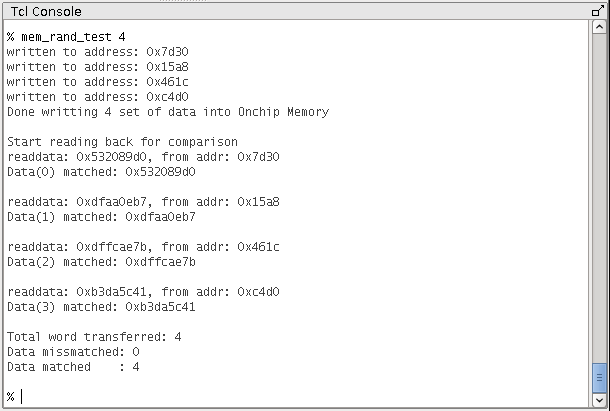

Exercising Onchip RAM

The GHRD contains an FPGA Onchip memory soft IP core. The System Console TCL script includes a simple memory test routine that writes some values to random memory locations and reads them back to verify they are correct. In order to run the memory test for 4 locations, type the following command in the System Console:mem_rand_test 4

© 1999-2024 RocketBoards.org by the contributing authors. All material on this collaboration platform is the property of the contributing authors.

This website is using cookies. More info.

That's Fine

RocketBoards

RocketBoards