Introduction

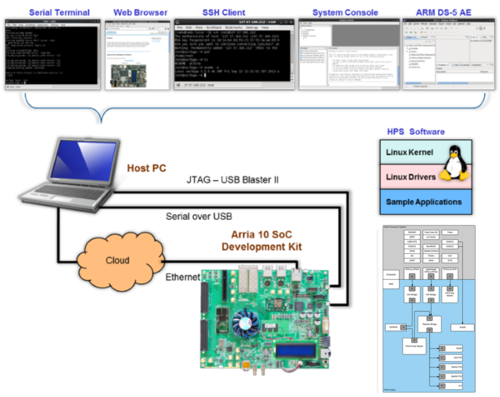

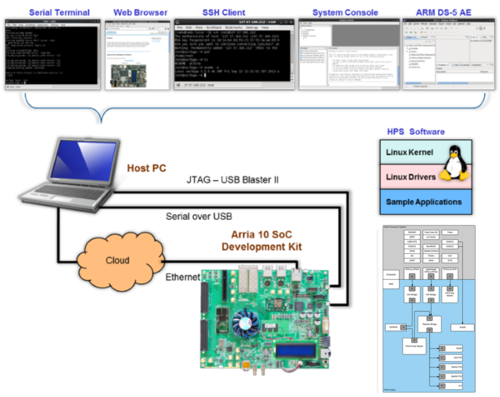

The Arria 10 SGMII reference design provides a set of essential hardware and software system components that can be used as a starting point for various custom user designs.

Getting Started Guides

SGMII Overview

The A10 SGMII RD consists of:

- Arria 10 SoC Development Board Rev C

- SGMII Hardware Reference Design

- Linux release

Release Notes, Release Contents and Release Tags

The latest release notes, contents and tags can be found here:

Release Notes, Contents, Locations and Tags

Release Location

There would be no release for SD Image binaries in 18.0

There would be no release for SD Image binaries in 18.1

There would be no release for SD Image binaries in 19.1

See topic

Creating and Updating the SD Card for this design

Prerequisites

The following are required in order to be able to fully exercise the A10 SGMII RD:

- Host PC running Linux (CentOS 6.8 was tested to work)

- Intel Arria 10 SoC Development Board Rev C

- Intel SoC EDS v18.0

- Intel Quartus™ Prime v18.0 and later

Note that the Bootloader (U-Boot) compilation requires a Linux host PC. The rest of the operations can be performed on a Windows host PC also.

GHRD Overview

See

SGMII RD Overview.

Build Flow

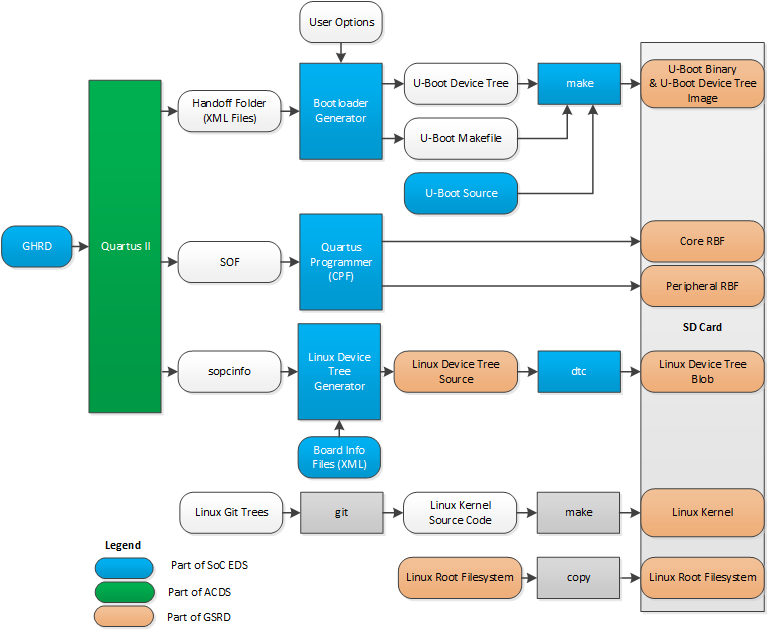

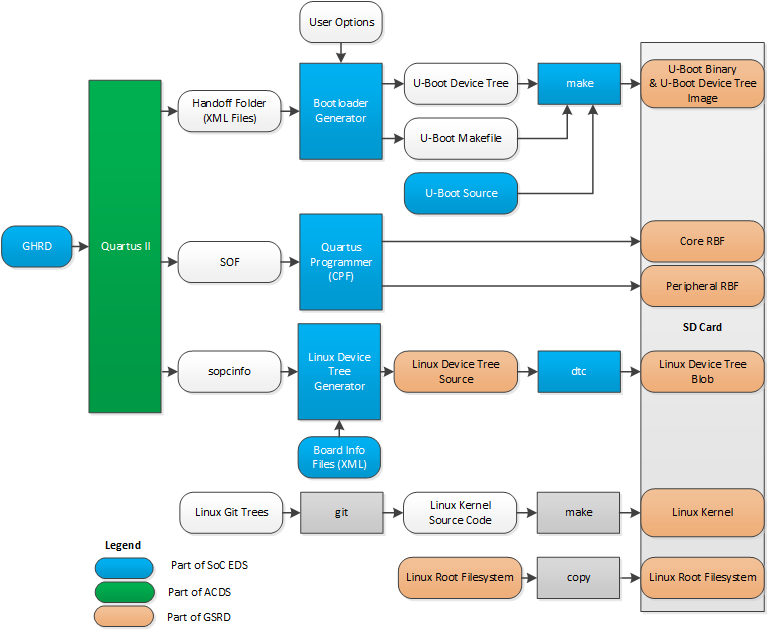

The following diagram illustrates the full build flow for the SGMII RD.

Important Note

Important Note: As shown above, on Arria 10 there are two different Device Trees: the one required by Bootloader (U-Boot), and another one required by the Linux Kernel.

The following table presents the tools that are used in the build flow:

| Tool |

Description |

Part of |

|---|

| Quartus Programmer |

Create, edit and compile FPGA hardware designs |

ACDS |

| Quartus Programmer CPF |

Utility that converts FPGA programming file from SOF to RBF format |

^ |

| Linux Device Tree Generator |

Generate Device Trees for Linux |

SoC EDS |

| dtc |

Device Tree Compiler, converts device tree source file to binary format (blob) |

^ |

| Bootloader Generator |

Generates Bootloader device tree and makefile based on hardware handoff information |

^ |

| ARM DS-5 AE |

Software Development Suite |

^ |

The following table presents the input files that are part of the build process:

| File |

Description |

|---|

| GHRD |

Quartus Project - FPGA Hardware Project source code |

| Board XML Files |

File describing the development board, used in creating the Device Tree |

| Linux Root Filesystem |

Prebuilt Linux root filesystem |

The following table describes the rest of the items that are part of the build flow diagram:

| File |

Description |

|---|

| .sof |

SRAM Object File - FPGA programming file, resulted from compiling the FPGA hardware project |

| .rbf |

Raw Binary File - Compressed FPGA programing file |

| .sopcinfo |

SOPC Info File - containing a description of the hardware to be used by Device Tree Generator |

| Handoff Folder |

Folder containing a description of the hardware to be used by the Bootloader Generator, in XML format |

Not all the people involved in a project need to deal with the full flow. For example:

- Board Designer: Typically works with the hardware engineer to decide the design of the custom board, pin muxing, and to update the Board XML file used by the Device Tree Generator.

- Hardware Engineer: Usually works only on the FPGA Quartus Project, and notifies the firmware engineer whenever the hardware files (.sof, .rbf, .sopcinfo, handoff folder) were changed. He also needs to notify the firmware engineer of any hardware interface changes.

- Firmware Engineer: Typically updates the Linux drivers according to the changes that were performed in hardware, recompiles the kernel if necessary. Re-generates the Device Tree when needed.

- Software Engineer: Develops the applications that run on top of the Linux OS. May need to change the software when new drivers are added.

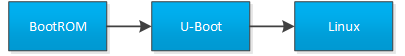

HPS Boot Flow

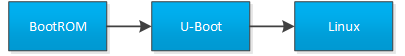

The SGMII RD boot flow includes the following stages:

- BootROM

- U-Boot

- Linux

The following table presents a short description of the different boot stages:

| Stage |

Description |

|---|

| BootROM |

Performs minimal configuration and loads U-Boot into 256KB OCRAM |

| U-boot |

Configures IO, FPGA, brings up DDRAM, loads Linux kernel |

| Linux |

Runs the end application |

For more information about Arria 10 SoC booting please refer to

Arria 10 Hard Processor System Technical Reference Manual, Booting and Configuration chapter.

A10 TSE Reference Design - Sustaining - User Manual

A10 TSE Reference Design - Sustaining - User Manual

Macnica Sulfur ~ Development Kit for Agilex™ 5 FPGA E-Series ~

Macnica Sulfur ~ Development Kit for Agilex™ 5 FPGA E-Series ~

Building Bootloader for Agilex 5

Building latest bootloaders for Agilex 5 SoC Devices

Building Bootloader for Agilex 5

Building latest bootloaders for Agilex 5 SoC Devices GSRD for Agilex 7 I-Series Transceiver-SoC DevKit (4x F-Tile)

Golden System Reference Design for DK SI AGI027FB, DK SI AGI027FA and DK SI AGI027FC

GSRD for Agilex 7 I-Series Transceiver-SoC DevKit (4x F-Tile)

Golden System Reference Design for DK SI AGI027FB, DK SI AGI027FA and DK SI AGI027FC The A10 SGMII RD consists of:

The A10 SGMII RD consists of:  Important Note: As shown above, on Arria 10 there are two different Device Trees: the one required by Bootloader (U-Boot), and another one required by the Linux Kernel.

The following table presents the tools that are used in the build flow:

Important Note: As shown above, on Arria 10 there are two different Device Trees: the one required by Bootloader (U-Boot), and another one required by the Linux Kernel.

The following table presents the tools that are used in the build flow:  The following table presents a short description of the different boot stages:

The following table presents a short description of the different boot stages:  RocketBoards

RocketBoards